## Computer aided design techniques for network-on-chip architectures ... Srinivasan, Krishnan

Dissertation Abstracts International; 2006; 67, 11; SciTech Premium Collection

## COMPUTER AIDED DESIGN TECHNIQUES FOR NETWORK-ON-CHIP ARCHITECTURES AND SYSTEM-LEVEL LOW POWER OPTIMIZATION

by

Krishnan Srinivasan

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

ARIZONA STATE UNIVERSITY

December 2006

UMI Number: 3241349

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform 3241349

Copyright 2007 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> **ProQuest Information and Learning Company** 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# COMPUTER AIDED DESIGN TECHNIQUES FOR NETWORK-ON-CHIP ARCHITECTURES AND SYSTEM-LEVEL LOW POWER OPTIMIZATION

by

Krishnan Srinivasan

has been approved

October 2006

| APPROVED:             |         |

|-----------------------|---------|

| P                     | , Chair |

| Sarma Mudleula        |         |

| Chaitali Chakrabarh   |         |

| So Ked                | •       |

| Suparticont Committee |         |

ACCEPTED:

Department Chair

Dean, Division of Graduate Studies

#### ABSTRACT

System-on-Chip (SoC) integrates several processing cores, ASIC blocks, memory, and communication elements on a single chip. The International Technology Roadmap for Semiconductors (ITRS) predicts that future generations of the high end SoC architectures will be implemented in less than 50nm technology, and clocked in the multi GHz range. These architectures will be composed of tens to hundreds of cores communicating with each other at several Gigabits per second.

Along with performance, power minimization will be an important design goal in nanoscale SoC architectures. Aggressive performance optimization and power minimization techniques will be applied by dividing these architectures into voltage and clock islands. These islands will operate on local clocks. Communication between the voltage islands, also known as global communication, will take place asynchronously, thus obviating the need for a global clock. Such architectures are known as Globally Asynchronous and Locally Synchronous (GALS) based systems.

This thesis addresses two important problems in GALS based SoC design: i) Design and optimization of global or inter-core communication architecture, and ii) system-level power minimization. As a primary contribution, the thesis addresses the optimization problems of the communication architecture in the context of a new communication paradigm to meet the performance requirements in future SoCs. As a secondary contribution, it addresses the problem of low power mapping and scheduling in multiprocessor SoC architecture. We propose mathematical models, heuristic techniques, and provably good polynomial time algorithms to solve the optimization problems of future SoC architectures.

Network-on-Chip (NoC) has been proposed as a solution for the global communication challenges in GALS based architectures. NoC supports asynchronous transfer of data, and given a suitable topology, can provide extremely high bandwidth by pipelining signal transmission, and by supporting concurrent communication. This thesis presents techniques for the design of low power NoC architectures, under performance constraints.

Dynamic voltage scaling (DVS), and dynamic power management (DPM) are two well known system-level power minimization schemes that are employed at the board level. GALS based SoC architectures will also support these power minimization techniques. The thesis presents techniques that integrate DVS and DPM with algorithmic transformations namely, pipelining and loop unrolling to minimize the power consumption of a multiprocessor GALS based architecture, under performance constraints.

To my parents

#### ACKNOWLEDGMENTS

I vividly remember the day when I stopped by Dr Chatha's office and talked to him about a possibility of a PhD under his supervision. Having him as a supervisor would have required that I change my major from Electrical Engg. to Computer Science. So, here I was, knocking on the door of a Professor just out of college, in a department alien to me. If I were to take such a risk today, I would certainly think twice, if not reject it right away. However, I am glad I took the risk. Most of the times, it is these seemingly innocuous decisions that cause major changes in a person's life. In my case, I am on the threshold of getting a PhD.

I would like to express my regards and thanks to my advisor, Dr. Karamvir S. Chatha for his continued guidance and support during my time in graduate school. Over the past four and a half years, he has helped me mature as a researcher, as well as an individual.

Thanks to Prof. Goran Konjevod for serving in my committee and giving me invaluable advice, specially pertaining to linear programming based algorithms.

My sincere thanks to Profs. Sarma Vrudhula and Chaitali Chakrabarti for serving in my committee and providing insights into my research.

Over the years, there have been so many members in the CSRL lab that it is impossible to list all of them. I have seen a lot of them graduate, and have been part of their joy and relief. Now that its my turn, I thank them for all the support and company. Be it intellectual discussion on research topics, or grappling about where to lunch, or the recent business competition, every single one of them has been a wonderful lab mate. Thanks guys!!!

In the first year of my PhD, I was desperately trying to obtain a linear programming solver.

And then one day, I went to Prof. Hans Mittelmann in the Department of Math. This thesis would not have been possible but for his help with linear programming solvers. Thanks Dr Mittelmann.

I have known Ms. Renate Mittelmann for over five years now. She let me use her lab space, and computers for my research. Her lab was particularly attractive due to the unlimited supply of chocolates and oranges (in winter). She is a wonderful human being, with whom I have always enjoyed talking. I thank her for all her support and encouragement during the course of my PhD.

My parents-in-law have waited patiently for more than a year for me to complete my PhD and get a job. I thank them for their support and prayers.

I would like to thank my brother Raman and sister-in-law Shantha for all their support. I owe everything I am today to my brother.

My sister Lakshmi and brother-in-law Ashutosh introduced me to the idea of a PhD at a very young age. In a way I got a head start, as I knew what to expect from a PhD at an age when most children did not know what PhD stood for. Thanks to you both for being the torch bearers of the family. You have been my role models.

My parents. Well, they have been with me all through. My brother summed it up when he said "They have not only given us our lives, but their lives as well".

Finally, my wife Rekha. She is the best thing that has happened to me.

#### TABLE OF CONTENTS

|    |      |        |                                                                          | Page |

|----|------|--------|--------------------------------------------------------------------------|------|

| LI | ST O | F TAB  | LES                                                                      | xiv  |

| LI | ST O | F FIGU | JRES                                                                     | xvi  |

| Cl | HAPT | ER     |                                                                          |      |

| 1  | INT  | RODU   | CTION                                                                    | 1    |

|    | 1.1. | Motiva | ation                                                                    | 1    |

|    | 1.2. | Summ   | ary of research contributions                                            | 4    |

|    |      | 1.2.1. | NoC design and optimization                                              | 4    |

|    |      | 1.2.2. | System-level low power optimization (VLSI Design 04: [1], ISVLSI 04 [2], |      |

|    |      |        | Integration, The VLSI Journal (Accepted))                                | 6    |

|    | 1.3. | Thesis | organization                                                             | 6    |

| 2  | APF  | PLICAT | TION SPECIFIC NOC DESIGN                                                 | 8    |

|    | 2.1. | Introd | uction                                                                   | 8    |

|    | 2.2. | NoC d  | lesign flow                                                              | 8    |

|    | 2.3. | Route  | r Architecture characterization                                          | 11   |

|    |      | 2.3.1. | Power consumption in input port of unit router                           | 13   |

|    |      | 2.3.2. | Power consumption in output port of unit router                          | 14   |

|    |      | 2.3.3. | Power consumption in physical links                                      | 15   |

|    |      | 2.3.4. | Latency                                                                  | 15   |

|    | 0.4  | D 11   | D.C. W.                                                                  | 10   |

| CI | IAP I | ER P                                                        | age |

|----|-------|-------------------------------------------------------------|-----|

|    | 2.5.  | Conclusion                                                  | 17  |

| 3  | LIT   | ERATURE SURVEY                                              | 19  |

|    | 3.1.  | Introduction                                                | 19  |

|    | 3.2.  | Seminal work                                                | 19  |

|    | 3.3.  | NoC architectures                                           | 20  |

|    |       | 3.3.1. Architectures for best effort traffic                | 20  |

|    |       | 3.3.2. Architectures for guaranteed throughput traffic      | 20  |

|    |       | 3.3.3. Architectures with error control schemes             | 21  |

|    |       | 3.3.4. Architectural optimizations for low power            | 21  |

|    | 3.4.  | Performance Evaluation                                      | 21  |

|    | 3.5.  | Automated design techniques                                 | 22  |

| 4  | INT   | EGER LINEAR PROGRAMMING BASED TECHNIQUES FOR APPLICATION    |     |

|    | SPE   | CIFIC NOC DESIGN                                            | 24  |

|    | 4.1.  | Introduction                                                | 24  |

|    | 4.2.  | ILP formulations                                            | 25  |

|    |       | 4.2.1. System-level floorplanning                           | 26  |

|    |       | 4.2.2. Custom interconnection topology and route generation | 30  |

|    | 4.3.  | Clustering based heuristic technique                        | 40  |

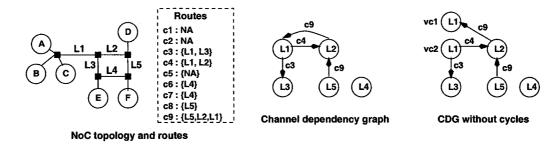

|    | 4.4.  | Deadlock avoidance                                          | 42  |

|    | 4.5.  | Results                                                     | 44  |

|    |       | 4.5.1. Benchmark applications                               | 44  |

|    |       | 4.5.2. Experimental setup                                   | 44  |

| CI | 1APT | ER                                                         | age |

|----|------|------------------------------------------------------------|-----|

|    |      | 4.5.3. Results and discussion                              | 47  |

|    | 4.6. | Conclusion                                                 | 52  |

| 5  | LOV  | V COMPLEXITY HEURISTICS FOR DESIGN OF CUSTOM NOC ARCHITEC- |     |

|    | TUF  | RES                                                        | 54  |

|    | 5.1. | Introduction                                               | 54  |

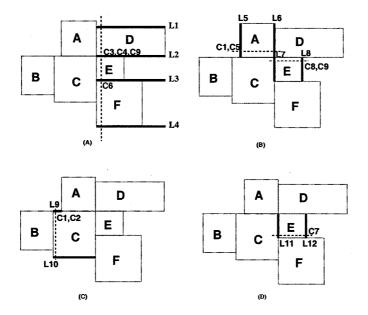

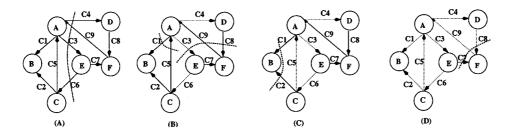

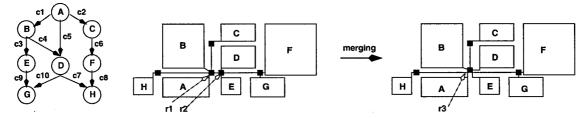

|    | 5.2. | Heuristic for Interconnection network generation           | 54  |

|    |      | 5.2.1. Link placement and trace mapping                    | 56  |

|    |      | 5.2.2. Core to router mapping                              | 59  |

|    |      | 5.2.3. Topology generation                                 | 60  |

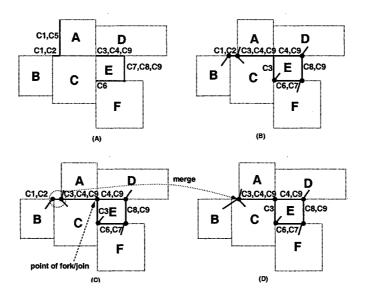

|    |      | 5.2.4. Router merging                                      | 61  |

|    | 5.3. | Complexity analysis                                        | 63  |

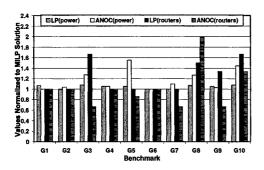

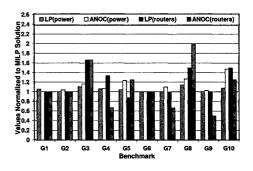

|    | 5.4. | Experimental results                                       | 64  |

|    |      | 5.4.1. Benchmark applications                              | 65  |

|    |      | 5.4.2. Experimental setup and result analysis              | 65  |

|    | 5.5. | Conclusion                                                 | 71  |

| 6  | APF  | PROXIMATION ALGORITHMS FOR MAPPING AND ROUTING PROBLEMS    |     |

|    | DUI  | RING NOC DESIGN                                            | 72  |

|    | 6.1. | Introduction                                               | 72  |

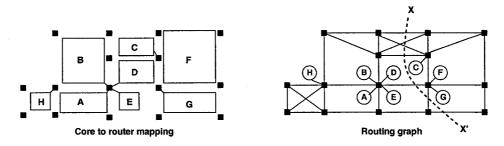

|    | 6.2. | Core to router mapping                                     | 73  |

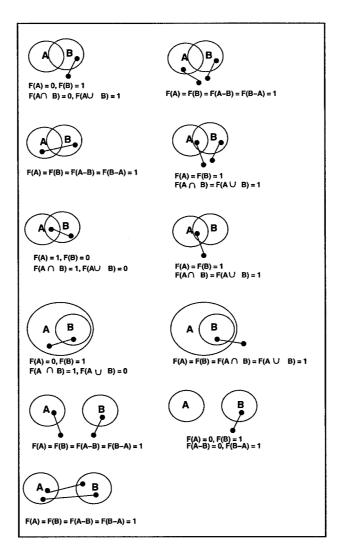

|    |      | 6.2.1. Equivalence to max-flow min-cut problem             | 74  |

|    | 6.3. | Routing and topology generation                            | 76  |

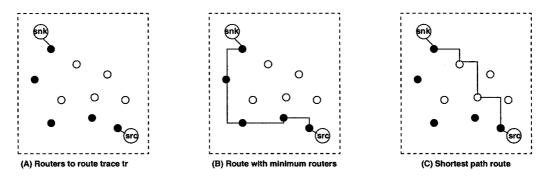

|    |      | 6.3.1 Topology generation with least number of routers     | 70  |

| CI | AAPI | EK     |                                                                            | Page  |

|----|------|--------|----------------------------------------------------------------------------|-------|

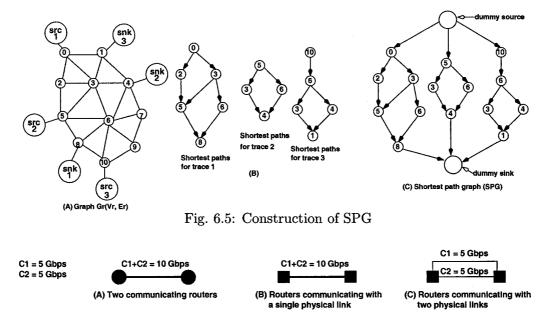

|    |      | 6.3.2. | NoC topologies with minimum power consumption                              | . 87  |

|    |      | 6.3.3. | Satisfying bandwidth constraints                                           | . 89  |

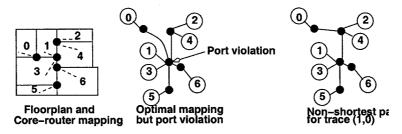

|    |      | 6.3.4. | Satisfying port constraints                                                | . 90  |

|    |      | 6.3.5. | Router merging                                                             | . 93  |

|    | 6.4. | Result | s                                                                          | . 94  |

|    |      | 6.4.1. | Benchmark applications                                                     | . 95  |

|    |      | 6.4.2. | Experimental setup                                                         | . 96  |

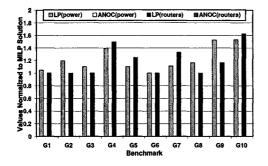

|    |      | 6.4.3. | Analysis and discussion                                                    | . 97  |

|    | 6.5. | Conclu | usion                                                                      | . 101 |

| _  | a Ta | TORTO  | AT CODE THE TOTAL PARTY OF THE TOTAL PROPERTY.                             | 100   |

| 7  | GEN  | NETIC  | ALGORITHM BASED TECHNIQUE FOR NOC DESIGN                                   | . 103 |

|    | 7.1. | Introd | uction                                                                     | . 103 |

|    | 7.2. | Geneti | ic algorithm for NoC topology design and route generation                  | . 104 |

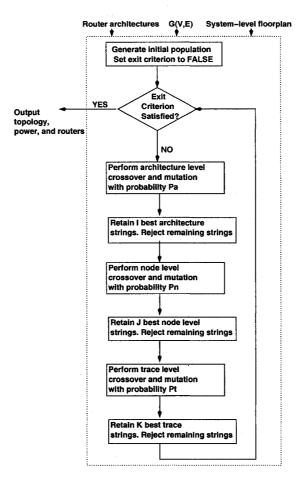

|    |      | 7.2.1. | Overview of GA                                                             | . 106 |

|    |      | 7.2.2. | Data structures for representation of solution                             | . 107 |

|    |      | 7.2.3. | Legality criteria for solution representation                              | . 110 |

|    |      | 7.2.4. | Generation of initial population and modified shortest path algorithm (MSI | P)112 |

|    |      | 7.2.5. | Pareto points and fitness calculation                                      | . 116 |

|    |      | 7.2.6. | Overview of the optimization technique                                     | . 117 |

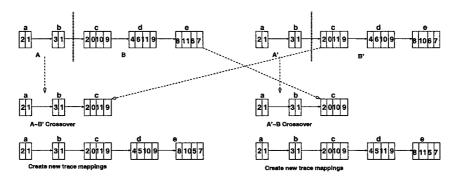

|    |      | 7.2.7. | Genetic operators                                                          | . 119 |

|    |      | 7.2.8. | Post-synthesis floorplan adjustment                                        | . 123 |

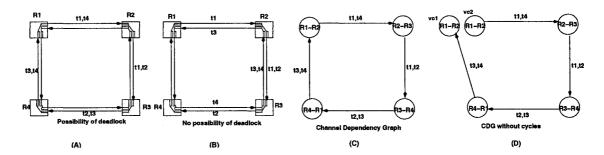

|    |      | 7.2.9. | Deadlock avoidance                                                         | . 124 |

|    | 7.3. | Result | SS                                                                         | . 127 |

| CI | HAPT | ER     |                                                                             | Page  |

|----|------|--------|-----------------------------------------------------------------------------|-------|

|    |      | 7.3.1. | Benchmark applications                                                      | . 127 |

|    |      | 7.3.2. | Experimental setup                                                          | . 128 |

|    |      | 7.3.3. | GA tuning parameters                                                        | . 129 |

|    |      | 7.3.4. | Results and discussion                                                      | . 130 |

|    | 7.4. | Conch  | usion                                                                       | . 145 |

| 8  | INT  | EGER   | LINEAR PROGRAMMING AND HEURISTICS FOR LOW POWER MAI                         | P_    |

| -  |      |        | O SCHEDULING FOR MULTIPROCESSOR ARCHITECTURES, UNDE                         |       |

|    | THE  | ROUGE  | IPUT CONSTRAINTS                                                            | . 146 |

|    | 8.1. | Introd | uction                                                                      | . 146 |

|    |      | 8.1.1. | Embedded multiprocessor architecture                                        | . 148 |

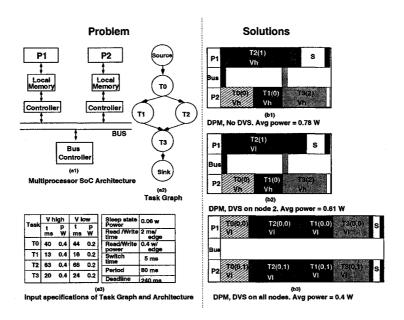

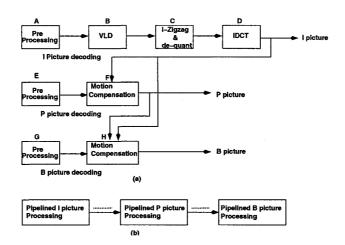

|    |      | 8.1.2. | Motivating Example                                                          | . 150 |

|    |      | 8.1.3. | Our Contributions                                                           | . 152 |

|    | 8.2. | Previo | ous Work                                                                    | . 153 |

|    |      | 8.2.1. | Power minimization in uni-processor systems                                 | . 153 |

|    |      | 8.2.2. | Power minimization in multiprocessor systems                                | . 154 |

|    |      | 8.2.3. | Low power scheduling in high-level synthesis                                | . 155 |

|    |      | 8.2.4. | Algorithmic transformations for system-level low power design               | . 155 |

|    | 8.3. | MILP   | Formulations for System Level Low Power Design                              | . 156 |

|    |      | 8.3.1. | Problem Definition                                                          | . 156 |

|    |      | 8.3.2. | The MILP formulation for optimal solution                                   | . 158 |

|    |      | 8.3.3. | MILP formulation that assumes a constant switching overhead ( $MILP_{so}$ ) | . 173 |

|    |      | 8.3.4. | MILP formulation that maximizes task run time $(MILP_{lat})$                | . 173 |

| CI           | HAPT  | ER     |                                                                                                                               | Page  |

|--------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------|-------|

|              |       | 8.3.5. | MILP formulation combining $MILP_{lat}$ and $MILP_{so}$ ( $MILP_{ls}$ )                                                       | . 174 |

|              | 8.4.  | Heuris | stic Techniques for System-level Low Power Design                                                                             | . 174 |

|              |       | 8.4.1. | Overview of the loop transformation algorithms                                                                                | . 174 |

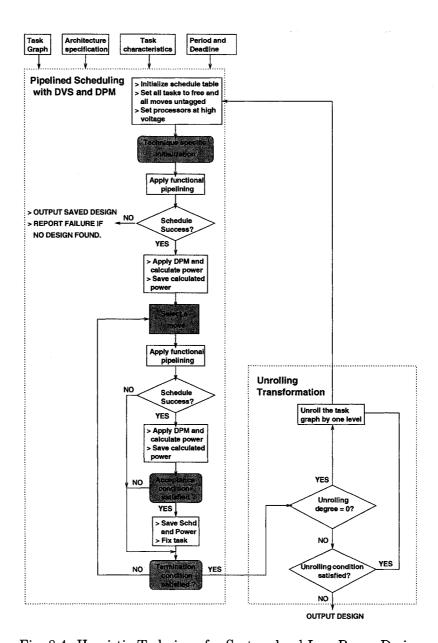

|              |       | 8.4.2. | Overall heuristic for system-level low power design                                                                           | . 175 |

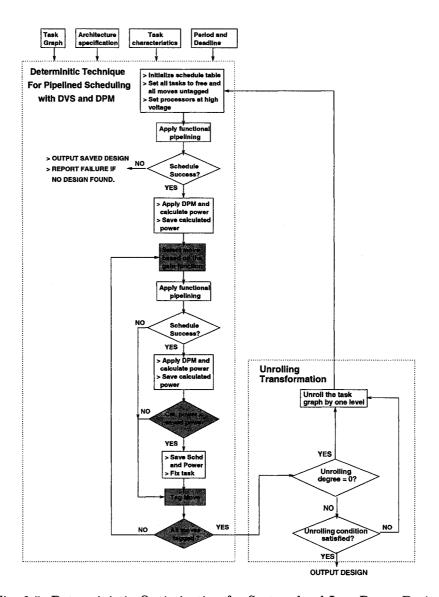

|              |       | 8.4.3. | Deterministic optimization for system-level low power design                                                                  | . 179 |

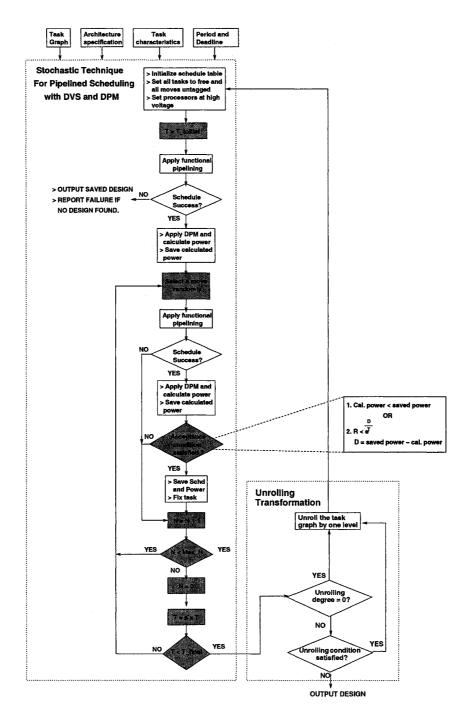

|              |       | 8.4.4. | Simulated annealing based optimization for Low Power Design                                                                   | . 182 |

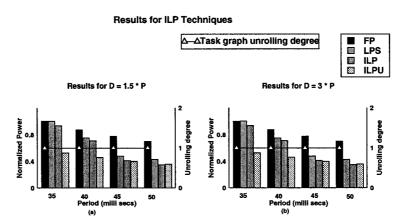

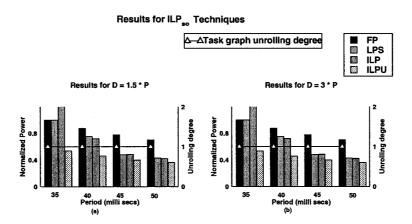

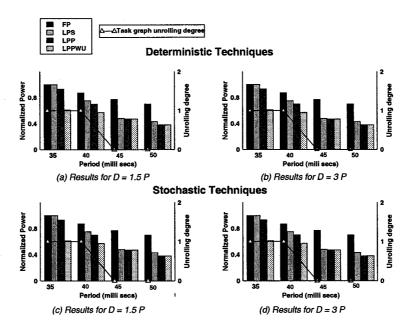

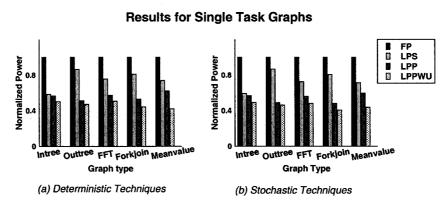

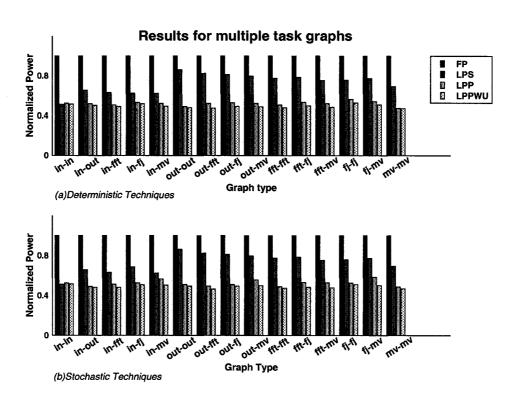

|              | 8.5.  | Result | ts                                                                                                                            | . 184 |

|              |       | 8.5.1. | Experimental set-up                                                                                                           | . 185 |

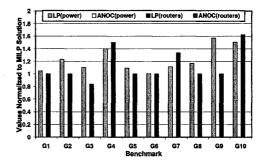

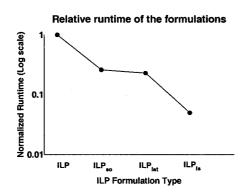

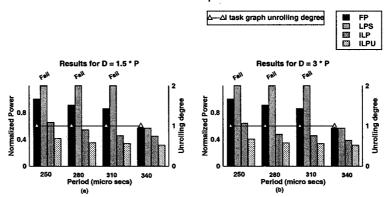

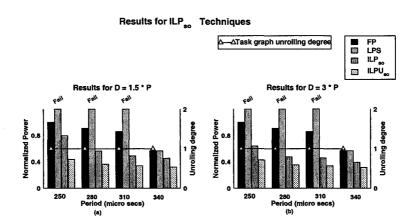

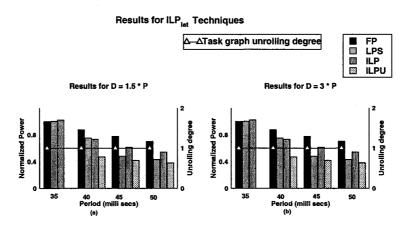

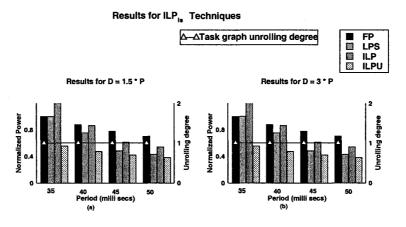

|              |       | 8.5.2. | Evaluation of MILP formulations                                                                                               | . 188 |

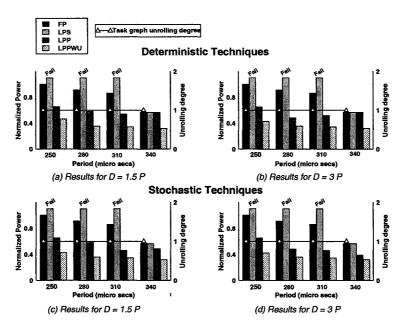

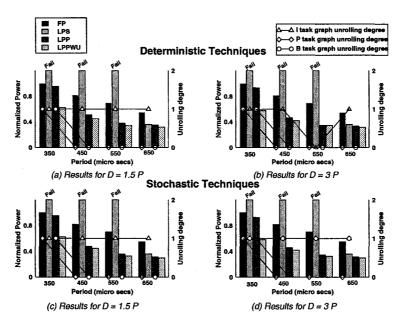

|              |       | 8.5.3. | Evaluation of heuristic techniques                                                                                            | . 191 |

|              | 8.6.  | Concl  | $ \text{usion}  \dots $ | . 194 |

| 9            | COI   | NCLUS  | ION                                                                                                                           | . 195 |

|              | 9.1.  | Applio | cation specific NoC design                                                                                                    | . 195 |

|              |       | 9.1.1. | Comparison of the different NoC design techniques                                                                             | . 195 |

|              |       | 9.1.2. | Discussion and future directions                                                                                              | . 196 |

|              | 9.2.  | System | m-level power minimization                                                                                                    | . 199 |

| Aj           | ppend | ix A . |                                                                                                                               | . 200 |

| $\mathbf{R}$ | EFER  | ENCE   | S                                                                                                                             | . 209 |

#### LIST OF TABLES

| Table |                                                                                | Page  |

|-------|--------------------------------------------------------------------------------|-------|

| 1     | Graph Characteristics                                                          | . 44  |

| 2     | Node descriptions                                                              | . 45  |

| 3     | Results for Floorplanning                                                      | . 45  |

| 4     | Comparison of ILP, and Clustering                                              | . 46  |

| 5     | Comparison of Clustering, and Mesh                                             | . 46  |

| 6     | Comparison of Clustering, and QNoC                                             | . 47  |

| 7     | Comparison of Clustering final solution with ILP and Clustering lower bounds . | . 47  |

| 8     | Benchmarks                                                                     | . 64  |

| 9     | Techniques                                                                     | . 64  |

| 10    | Node descriptions for MPEG and MWD                                             | . 69  |

| 11    | Node description for Set-top box                                               | . 69  |

| 12    | Benchmarks                                                                     | . 95  |

| 13    | Average power and router consumption                                           | . 97  |

| 14    | Runtimes                                                                       | . 97  |

| 15    | Node description for Set-top box, and NP                                       | . 99  |

| 16    | Benchmarks                                                                     | . 129 |

| 17    | Technique nomenclature                                                         | . 130 |

| 18    | Average power and router consumption                                           | . 134 |

| 19    | Runtimes                                                                       | . 134 |

| 20    | Nomenclature of variables                                                      | . 159 |

| 21    | Summary of results for MILP                                                    | 188   |

| able |                                                                                   | 'age |

|------|-----------------------------------------------------------------------------------|------|

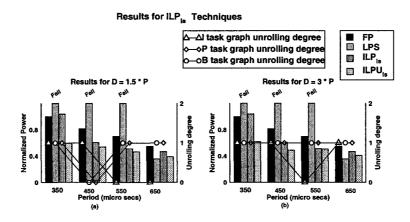

| 22   | Summary of results for $MILP_{so}$                                                | 188  |

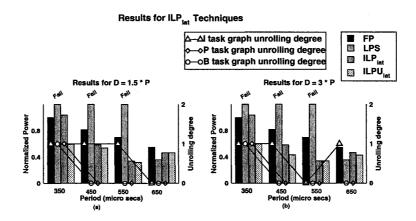

| 23   | Summary of results for $MILP_{lat}$                                               | 188  |

| 24   | Summary of results for $MILP_{ls}$                                                | 188  |

| 25   | Comparison of deterministic technique with other heuristic techniques             | 192  |

| 26   | Comparison of simulated annealing based technique with other heuristic techniques | 192  |

| 27   | Comparison between heuristic and optimum MILP based techniques                    | 192  |

| 28   | Comparison of all techniques for multimedia applications                          | 192  |

| 29   | Average power and router consumption                                              | 196  |

| 30   | Runtimes                                                                          | 196  |

### LIST OF FIGURES

| Figure |                                                     | Page |

|--------|-----------------------------------------------------|------|

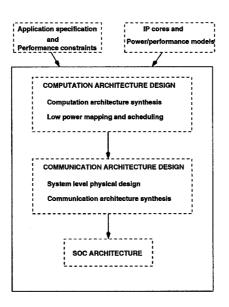

| 1.1    | Application specific SoC architecture design        | . 3  |

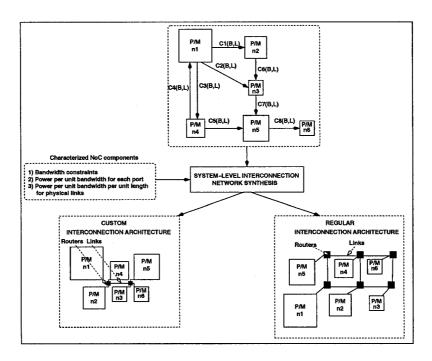

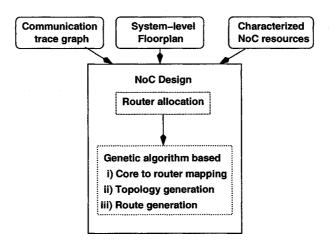

| 2.1    | NoC architecture design                             | . 9  |

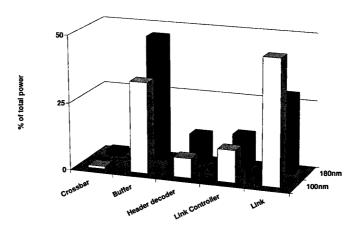

| 2.2    | Power consumption of NoC                            | . 10 |

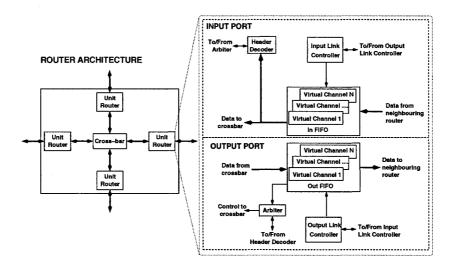

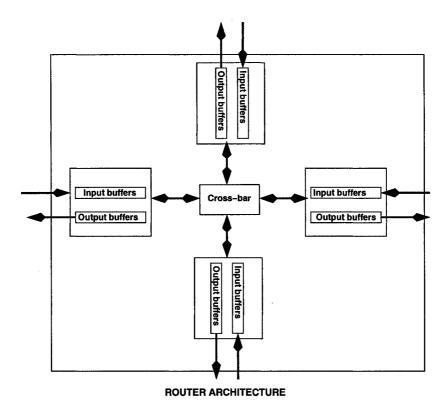

| 2.3    | NoC router architecture                             | . 12 |

| 2.4    | Input port power consumption set-up                 | . 13 |

| 2.5    | Output port power consumption set-up                | . 13 |

| 2.6    | Input port power consumption                        | . 14 |

| 2.7    | Output port power consumption                       | . 14 |

| 2.8    | Link power versus injection rate                    | . 14 |

| 2.9    | Link power versus length                            | . 15 |

| 2.1    | 0 Latency for 2 routers                             | . 15 |

| 2.1    | 1 Latency for 4x4 mesh                              | . 15 |

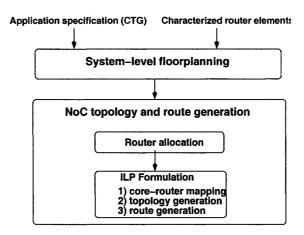

| 4.1    | ILP based NoC generation                            | . 25 |

| 4.2    | Example mesh based floorplan                        | . 29 |

| 4.3    | Illegal layout in mesh based topology               | . 29 |

| 4.4    | Example of router allocation for custom topology    | . 32 |

| 4.5    | Algorithm for removing redundant routers            | . 32 |

| 4.6    | Adding router to increase number of traffic         | . 39 |

| 4.7    | Clustering based approach                           | . 41 |

| 4.8    | Breaking deadlocks with additional virtual channels | . 42 |

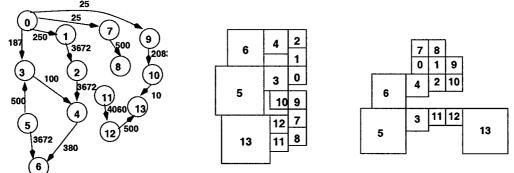

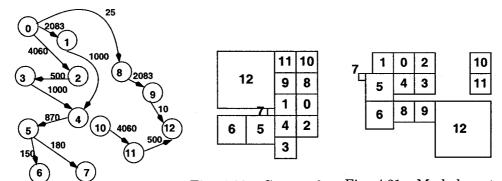

| 4.9    | 263 dec mp3 dec: Communication Trace Graph          | . 49 |

| Figure                                                      | Page |

|-------------------------------------------------------------|------|

| 4.10 Custom layout for 263 dec mp3 dec                      | 49   |

| 4.11 Mesh layout for 263 dec mp3 dec                        | 49   |

| 4.12 5 port topology for 263 dec mp3 dec                    | 49   |

| 4.13 4 port topology for 263 dec mp3 dec                    | 49   |

| 4.14 263 enc mp3 dec:Communication Trace Graph              | 50   |

| 4.15 Custom layout for 263 enc mp3 dec                      | 50   |

| 4.16 Mesh layout for 263 enc mp3 dec                        | 50   |

| 4.17 5 port topology for 263 enc mp3 dec                    | 50   |

| 4.18 4 port topology for 263 enc mp3 dec                    | 50   |

| 4.19 mp3 enc mp3 dec:Communication Trace Graph              | 51   |

| 4.20 Custom layout for mp3 enc mp3 dec                      | 51   |

| 4.21 Mesh layout for mp3 enc mp3 dec                        | 51   |

| 4.22 5 port topology for mp3 enc mp3 dec                    | 51   |

| 4.23 4 port topology for mp3 enc mp3 dec                    | 51   |

| 5.1 ANOC design flow                                        | 55   |

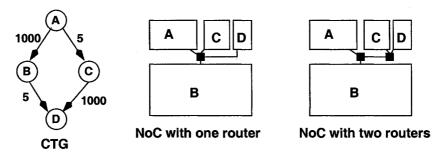

| 5.2 CTG, floorplan and channel intersection graph           | 55   |

| 5.3 Recursive partitioning link placement and trace mapping | 57   |

| 5.4 Recursive cuts on the CTG                               | 57   |

| 5.5 Topology generation and router merging                  | 60   |

| 5.6 Router merging                                          | 61   |

| 5.7 Interconnection network generation                      | 63   |

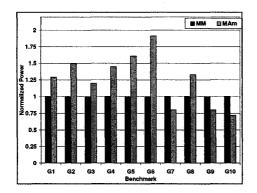

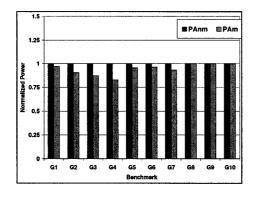

| 5.8 Power comparison between $MM$ and $MA_m$                | 66   |

| Figure           |                                                                     | Page |

|------------------|---------------------------------------------------------------------|------|

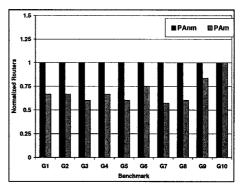

| 5.9 I            | Router comparison between $MM$ and $MA_m$                           | . 66 |

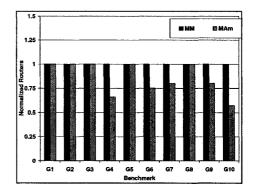

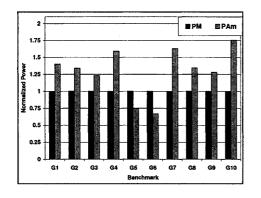

| 5.10 I           | Power comparison between $PM$ and $PA_m$                            | . 66 |

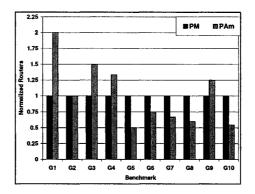

| 5.11 I           | Router comparison between $PM$ and $PA_m$                           | . 66 |

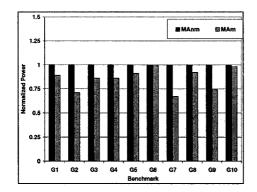

| 5.12 I           | Power comparison between $MA_m$ and $MA_{nm}$                       | . 67 |

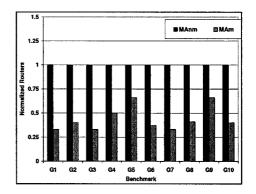

| 5.13 I           | Router comparison between $MA_m$ and $MA_{nm}$                      | . 67 |

| 5.14 I           | Power comparison between $PA_m$ and $PA_{nm}$                       | . 67 |

| 5.15 I           | Router comparison between $PA_m$ and $PA_{nm}$                      | . 67 |

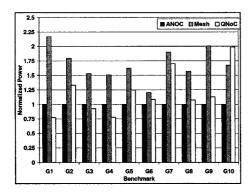

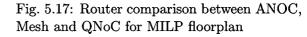

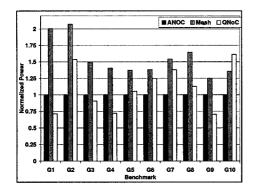

| 5.16 I           | Power comparison between ANOC, Mesh and QNoC for MILP floorplan     | . 68 |

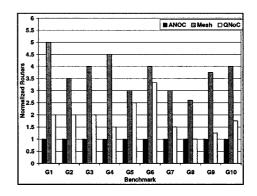

| 5.17 I           | Router comparison between ANOC, Mesh and QNoC for MILP floorplan    | . 68 |

| 5.18 I           | Power comparison between ANOC, Mesh and QNoC for Parquet floorplan  | . 68 |

| 5.19 I           | Router comparison between ANOC, Mesh and QNoC for Parquet floorplan | . 68 |

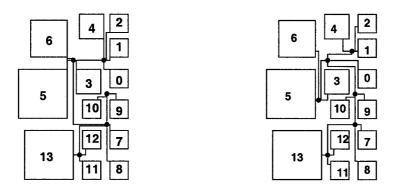

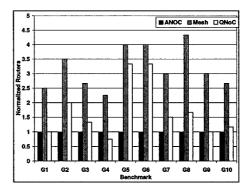

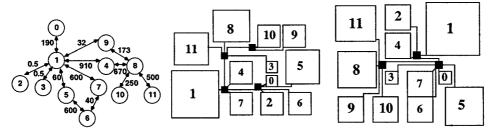

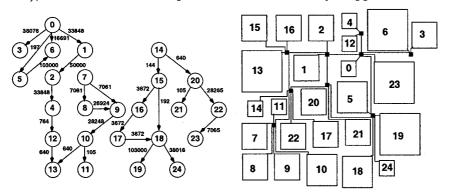

| 5.20 I           | MPEG4 CTG                                                           | . 70 |

| 5.21             | $MA_m$ MPEG4 topology                                               | . 70 |

| 5.22 $1$         | $PA_m$ MPEG4 topology                                               | . 70 |

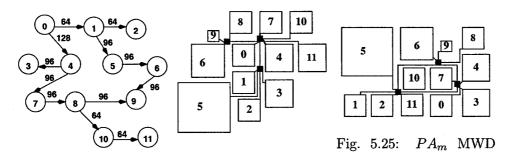

| 5.23 I           | MWD CTG                                                             | . 70 |

| $5.24$ $\lambda$ | $MA_m$ MWD topology                                                 | . 70 |

| $5.25$ $\lambda$ | $PA_m$ MWD topology                                                 | . 70 |

| 5.26             | CTG for set-top box application                                     | . 70 |

| 5.27 I           | Floorplan and interconnection network architecture                  | . 70 |

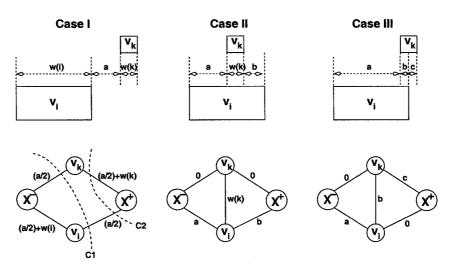

| 6.1              | Core alignments and flow graphs                                     | . 74 |

| 6.2              | Topology design                                                     | . 79 |

| 6.3 I            | Proof of supermodularity                                            | . 82 |

| Figure |                                                                                  | Page  |

|--------|----------------------------------------------------------------------------------|-------|

| 6.4    | Routing with shortest path and minimum routers                                   | . 84  |

| 6.5    | Construction of SPG                                                              | . 87  |

| 6.6    | Logical versus physical routing                                                  | . 87  |

| 6.7    | Resolving infeasible solutions due to port constraints                           | . 92  |

| 6.8    | Router merging                                                                   | . 92  |

| 6.9    | Power and router comparisons with no port and no link constraints                | . 98  |

| 6.10   | Power and router comparisons with no port constraint but with link constraints . | . 98  |

| 6.11   | Power and router comparisons with port constraints but no link constraints. ANOC |       |

|        | violated port constraints for all benchmarks and is not plotted                  | . 98  |

| 6.12   | Power and router comparisons with power and router constraints. ANOC violated    |       |

|        | port constraints for all benchmarks and is not plotted                           | . 98  |

| 6.13   | Minimizing power consumption by introducing additional routers                   | . 99  |

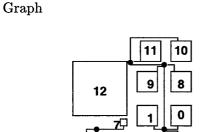

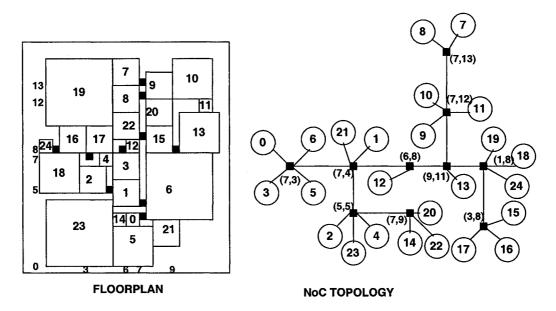

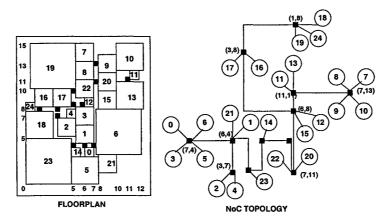

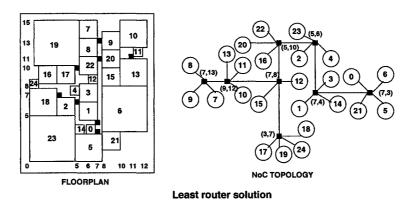

| 6.14   | Floorplan and NoC topology for Set-top box                                       | . 100 |

| 6.15   | Floorplan and NoC topology for NP                                                | . 101 |

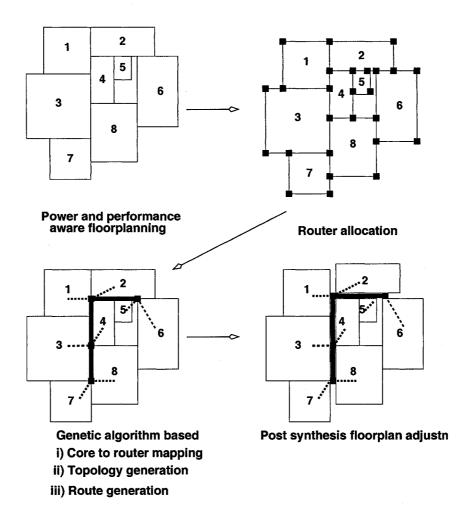

| 7.1    | Application specific NoC design flow                                             | . 104 |

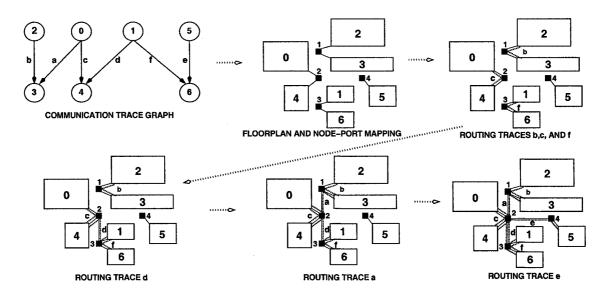

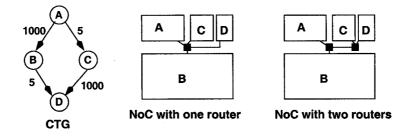

| 7.2    | Example NoC design flow                                                          | . 105 |

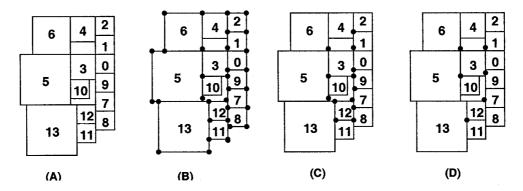

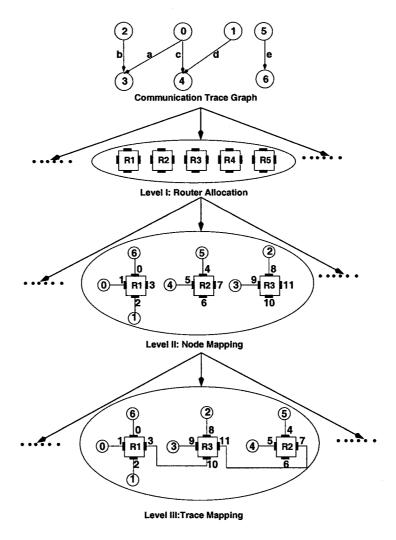

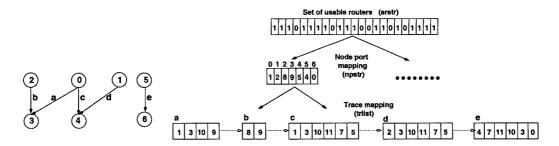

| 7.3    | Hierarchical representation                                                      | . 107 |

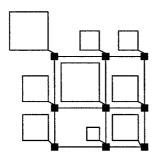

| 7.4    | Array based data-structure                                                       | . 108 |

| 7.5    | Communication trace mapping                                                      | . 113 |

| 7.6    | Pseudo code for MSP algorithm                                                    | . 114 |

| 7.7    | Pareto points for NoC generation                                                 | . 115 |

| 7.8    | GA for custom NoC design                                                         | . 118 |

| Figure                                                                                                                   | ;e |

|--------------------------------------------------------------------------------------------------------------------------|----|

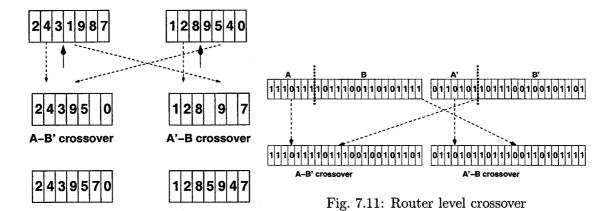

| 7.9 Trace level crossover                                                                                                | 9  |

| 7.10 Node level crossover                                                                                                | 0  |

| 7.11 Router level crossover                                                                                              | 0  |

| 7.12 Router architecture                                                                                                 | 5  |

| 7.13 Breaking deadlocks by adding virtual channels                                                                       | 6  |

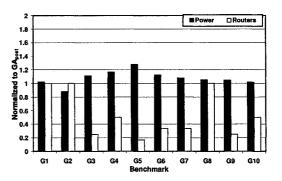

| 7.14 Comparison between $GA_{6,5}$ , $ILP_{6,5}$ and $ANOC_{6,5}$ corresponding to minimum                               |    |

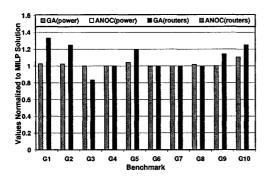

| power consumption. ANOC caused port violations for all benchmarks                                                        | 1  |

| 7.15 Comparison between $GA_{6,5}$ , $ILP_{6,5}$ and $ANOC_{6,5}$ corresponding to solution with                         |    |

| minimum router resource consumption. ANOC caused port violations for all bench-                                          |    |

| marks                                                                                                                    | 1  |

| 7.16 Comparison between $GA_{6,\infty}$ , $ILP_{6,\infty}$ and $ANOC_{6,\infty}$ corresponding to minimum                |    |

| power consumption                                                                                                        | 2  |

| 7.17 Comparison between $GA_{6,\infty}$ , $ILP_{6,\infty}$ and $ANOC_{6,\infty}$ corresponding to solution with          |    |

| minimum router resource consumption                                                                                      | 2  |

| 7.18 Comparison between $GA_{\infty,5}$ , $ILP_{\infty,5}$ and $ANOC_{\infty,5}$ corresponding to minimum                |    |

| power consumption. ANOC caused port violations for all benchmarks                                                        | 3  |

| 7.19 Comparison between $GA_{\infty,5}$ , $ILP_{\infty,5}$ and $ANOC_{\infty,5}$ corresponding to solution               |    |

| with minimum router resource consumption. ANOC caused port violations for all                                            |    |

| benchmarks                                                                                                               | 3  |

| 7.20 Comparison between $GA_{\infty,\infty}$ , $ILP_{\infty,\infty}$ and $ANOC_{\infty,\infty}$ corresponding to minimum |    |

| power consumption                                                                                                        | 3  |

| Figure | Page |

|--------|------|

|        |      |

| 7.21 | Comparison between $GA_{\infty,\infty}$ , $ILP_{\infty,\infty}$ and $ANOC_{\infty,\infty}$ corresponding to solution |

|------|----------------------------------------------------------------------------------------------------------------------|

|      | with minimum router resource consumption                                                                             |

| 7.22 | Minimizing power consumption by introducing additional routers                                                       |

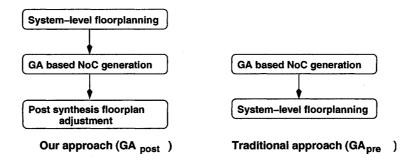

| 7.23 | Our approach versus existing approach                                                                                |

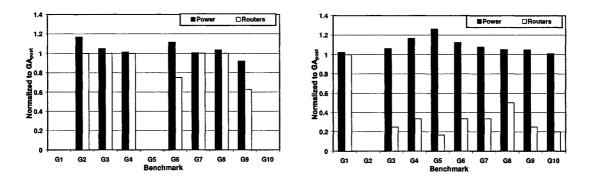

| 7.24 | Comparing $GA_{pre}$ and $GA_{post}$ for $GA_{6,5}$ . Existing approach caused link length                           |

|      | violations for benchmarks 1, 5 and 10                                                                                |

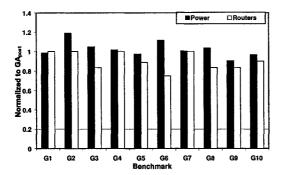

| 7.25 | Comparing $GA_{pre}$ and $GA_{post}$ for $GA_{6,\infty}$ . Existing approach caused link length                      |

|      | violations for benchmark 2                                                                                           |

| 7.26 | Comparing $GA_{pre}$ and $GA_{post}$ for $GA_{\infty,5}$                                                             |

| 7.27 | Comparing $GA_{pre}$ and $GA_{post}$ for $GA_{\infty,\infty}$                                                        |

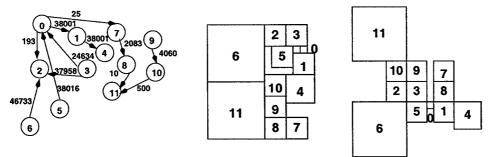

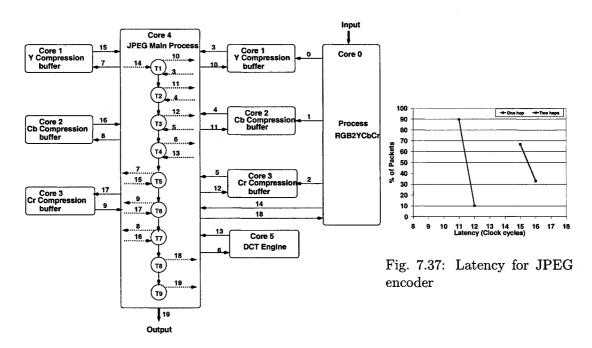

| 7.28 | CTG for JPEG encoder                                                                                                 |

| 7.29 | Node description for set-top box, NP, and JPEG                                                                       |

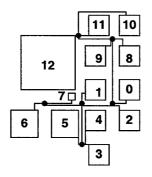

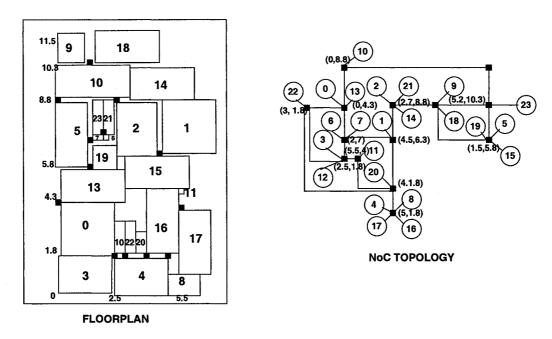

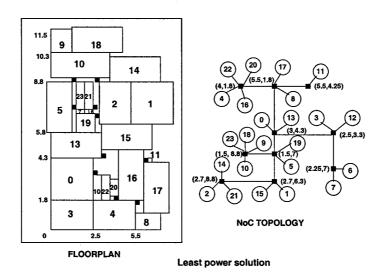

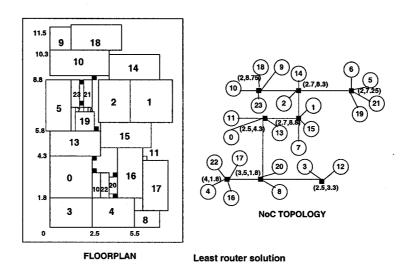

| 7.30 | Floorplan and NoC topology for set-top box                                                                           |

| 7.31 | Floorplan and NoC topology for NP                                                                                    |

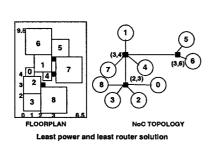

| 7.32 | Floorplan and NoC topology for JPEG encoder                                                                          |

| 7.33 | Pareto curve for the JPEG, NP and set-top box applications                                                           |

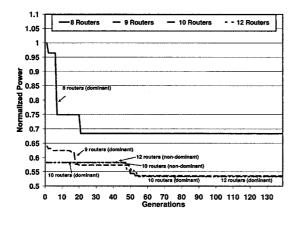

| 7.34 | Power consumption across generations                                                                                 |

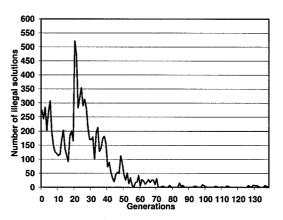

| 7.35 | Number of illegal solutions across generations                                                                       |

| 7.36 | JPEG process graph                                                                                                   |

| 7.37 | Latency for JPEG encoder                                                                                             |

| 8.1  | Motivating Example                                                                                                   |

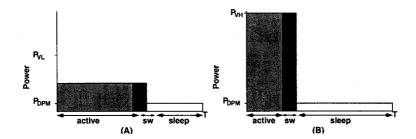

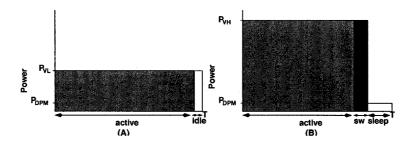

| 8.2  | Comparison of DVS policies: period constraint greater than task run time 16                                          |

| Figure |                                                                      | Page  |

|--------|----------------------------------------------------------------------|-------|

| 8.3    | Comparison of DVS policies: period constraint close to task run time | . 166 |

| 8.4    | Heuristic Technique for System-level Low Power Design                | . 176 |

| 8.5    | Deterministic Optimization for System-level Low Power Design         | . 180 |

| 8.6    | Simulated annealing based optimization for low power design          | . 183 |

| 8.7    | MPEG decoder task flow                                               | . 185 |

| 8.8    | JPEG decoder task flow                                               | . 185 |

| 8.9    | MP3 encoder task flow                                                | . 186 |

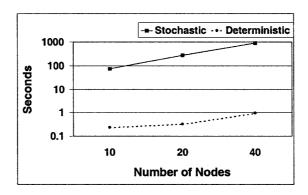

| 8.10   | Runtimes of the MILP formulations                                    | . 191 |

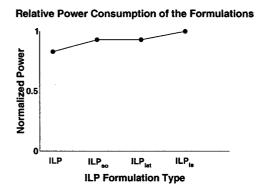

| 8.11   | Relative power consumption of the MILP formulations                  | . 191 |

| 8.12   | Runtimes of the heuristic techniques                                 | . 193 |

| A.1    | JPEG: Results for MILP                                               | . 200 |

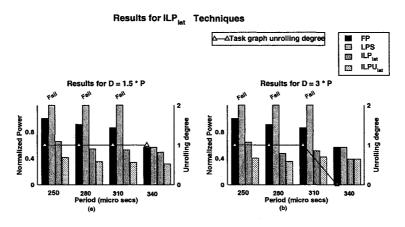

| A.2    | JPEG: Results for $MILP_{so}$                                        | . 201 |

| A.3    | JPEG: Results for the $MILP_{lat}$                                   | . 201 |

| A.4    | JPEG: Results for $MILP_{ls}$                                        | . 202 |

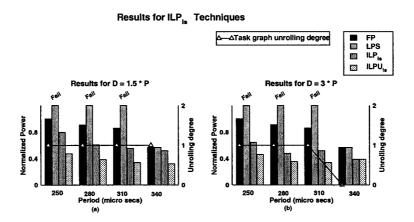

| A.5    | MPEG: Results for MILP                                               | . 202 |

| A.6    | MPEG: Results for the $MILP_{so}$                                    | . 203 |

| A.7    | MPEG: Results for $MILP_{lat}$                                       | . 203 |

| A.8    | MPEG: Results for $MILP_{ls}$                                        | . 203 |

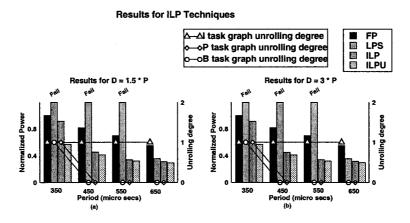

| A.9    | MP3: Results for MILP                                                | . 204 |

| A.10   | ) MP3: Results for the $MILP_{so}$                                   | . 204 |

| A.11   | MP3: Results for $MILP_{lat}$                                        | . 205 |

| A.12   | 2 MP3: Results for $MILP_{ls}$                                       | . 205 |

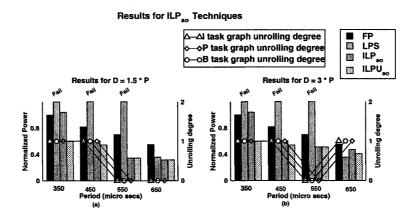

| Figure                                       | Page |

|----------------------------------------------|------|

| A.13 Heuristics: Results for JPEG decoding   | 206  |

| A.14 Heuristics: Results for MPEG-1 decoding | 206  |

| A.15 Heuristics: Results for MP3 encoding    | 207  |

| A.16 Single synthetic task graphs            | 207  |

| A.17 Multiple synthetic task graphs          | 208  |

xxiii

#### CHAPTER 1

#### INTRODUCTION

#### 1.1. Motivation

Increased power densities, high performance requirements, and short design turn-around times have prompted designers to integrate multiple processor cores and memory elements on the same chip, known as multiprocessor System-on-Chip (MPSoC). Many of these architectures are targeted toward custom applications such as multimedia set-top box and have come to be known as application specific SoC. In the future, these architectures will be composed of hundreds of cores, will be implemented in 50nm technology or lower, and will be clocked in multi-GHz range.

High performance requirements, and low power consumption constraints will be two important design challenges in future SoC architectures. High clock speeds and increasing clock skews will make synchronous communication undesirable, or even infeasible. SoC designers will aggressively apply system-level power minimization techniques namely, dynamic voltage scaling (DVS), and dynamic power management (DPM) for power minimization. The requirement for timing closure, and the need for optimizing the architecture for power and performance will move design techniques toward partitioning the system into multiple voltage and clock islands. These islands will be locally clocked, and communicate with each other in an asynchronous manner. Architectures supporting this type of communication are known as globally asynchronous and locally synchronous (GALS) architectures [3]. GALS based communication provides the flexibility required by the designer to optimize the architecture for power and performance. The voltage and frequency of each island can be locally optimized to satisfy performance requirements, and minimize power consumption.

GALS based SoC designs in nanoscale technologies will also be faced with several communication challenges. Global signal delays will span multiple clock cycles [4] [5]. Signal integrity would also suffer due to increased RLC effects. The poor scalability of bus based communica-

tion will make them undesirable for future multi-core architectures. As mentioned before, low power consumption under performance constraints will be a major design goal. Network-on-Chip (NoC) has been proposed as a solution to the global communication challenges for SoC design in nanoscale technologies [6] [7]. NoC supports asynchronous transfer of packets, and is a suitable communication paradigm in GALS based systems. Given a suitable topology, it can provide extremely high bandwidth by distributing the propagation delay across multiple switches, and thus pipelining the signal transmission. NoCs also offer advantages of supporting error control techniques, and supporting quality of service by distinguishing between different classes of traffic.

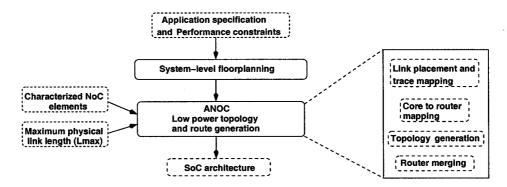

Figure 1.1 depicts the various steps involved in the design of an application specific SoC architecture. The SoC design problem can be broadly classified into two categories: i) computation architecture design, and ii) communication architecture design integrated with system-level physical design. The computation architecture design stage takes the application specification and performance constraints as input, and performs i) computation architecture synthesis, and ii) mapping and scheduling of the application on the processing cores. At the end of the computation architecture design stage, the application can be characterized, and communication patterns between the various cores of the architecture can be generated. The second step takes the communication traces as input, and generates a communication architecture that is optimized for a given design goal (for example, low power under performance constraints).

In this thesis, we address the power and performance optimization problems in the realm of GALS based application specific SoC architectures. We address the problems from computation, as well as the communication architecture design standpoints. At the computation architecture design stage, the architecture synthesis problem has been extensively investigated by several researchers [8] [9] [10]. On the other hand, low power mapping and scheduling is still an open problem. As mentioned before, SoC architecture design will move toward partitioning the system into voltage and clock islands. Optimized mapping and scheduling of the application to the

Fig. 1.1: Application specific SoC architecture design

different voltage islands is an important step in minimizing the computation architecture power.

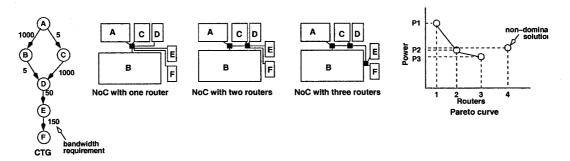

A NoC designer has to choose between utilizing a regular NoC architecture like a mesh or torus, or a custom architecture optimized for a given application. Regular architectures offer lower design time, and are useful when implemented in a generic multiprocessor environment such as the MIT RAW [11]. On the other hand, custom NoC architectures are designed with the given application in mind. For example, a NoC may be optimized for the MPEG-4 decoder application. In this thesis, we demonstrate that application specific architectures are superior to regular architectures in terms of power, performance and area.

In nanoscale technologies, link power will consume a considerable part of the total communication power [12]. In order to account for link power, system-level physical design must be integrated in the NoC design flow. NoCs designed for future SoC architectures will have to support the communication requirements between hundreds of cores. The complexity of designing a NoC that integrates system-level physical design, topology of the network, mapping of hundreds of cores and routing of communication traffic calls for efficient automated techniques for its

optimization.

#### 1.2. Summary of research contributions

The thesis addresses the NoC design and optimization, and system-level power minimization problems in the context of GALS based SoC architectures. The following sections summarize the contributions of the thesis toward each of the two problems.

#### 1.2.1. NoC design and optimization

In this thesis, we defined the problem of designing custom NoCs that are optimized for a given application domain. This is in contrast to the existing approach by other researchers who assume that the NoC topology has a regular structure (such as a mesh). Through extensive experiments on multimedia and network processing benchmarks, we have demonstrated that the NoCs that are optimized for the given application domain are better than regular NoCs in terms of power, performance and area.

In the context of application specific NoC design techniques, we have proposed four techniques, each of which trade-off the quality of the solution with the time required to arrive at the final solution. The proposed techniques are:

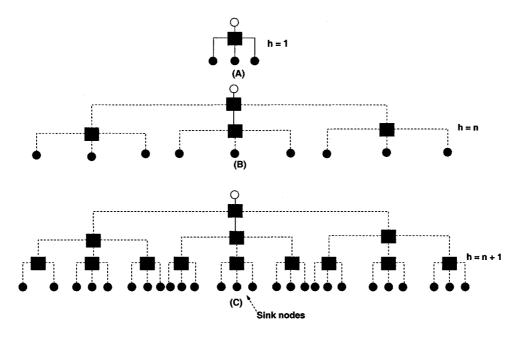

1. Integer Linear Programming (ILP) formulation, and clustering based heuristics (ICCD 04 [13], ISQED 06 [14], IEEE TVLSI 06 [12]): We formulated the NoC design problem as an ILP formulation. The ILP formulation is extremely useful as it has the ability to generate optimal solutions. The optimal solution also serves as an excellent benchmark to which the solutions generated by other heuristics can be compared. However, the complexity of the ILP is known to be exponential in the number of inputs. Therefore, the time taken to arrive at the final solution explodes with increasing size of the problem. In order to alleviate the large solution times, we proposed a clustering based heuristic that divides the problem into

smaller clusters, solves the clusters optimally, and generates the final solution by merging the clusters together.

- 2. Low complexity heuristic technique for NoC design (DATE 06 [15], ISPLED 05 [16], ISSS-CODES 06 [17], under review at ACM TODAES): We proposed a low complexity heuristic technique for custom NoC design that generates solutions for large problem sizes in negligible time. Due to its low complexity, the technique can be utilized as part of an iterative design space exploration for the design of application specific SoC architectures. We compared our heuristic with the optimal ILP based technique, and observed that the heuristic is able to generate solutions that are on average, within 1.25 of the optimal.

- 3. Approximation algorithms for NoC design (ICCAD 05 [18], ASPDAC 07 [19]): An approximation algorithm has the ability to generate solutions with known quality bound in polynomial time. Since the algorithm is polynomial time, it scales well with problem size. The approximation bound guarantees that the solution generated by the technique will never be worse than the bound. Approximation algorithms are immensely useful not only in the generation of good solutions, but also in serving as a benchmark for other techniques when the problem size is so large that the ILP based technique cannot be utilized. Our technique divides the NoC design problem into two phases, and generates solutions with quality bounds for each of the two phases.

- 4. Genetic algorithm based heuristic for NoC design (VLSI Design 05 [20] ASPDAC 05 [21], Under second round review at IEEE TVLSI): A Genetic Algorithm (GA) models the problem as a set of genetic strings that undergo genetic operations namely, crossover and mutation and evolve over successive generations. We model the NoC design problem as a GA in three levels of hierarchy. The GA serves as a trade-off between the high runtimes of the ILP based technique, and lower solution quality of the low complexity heuristics. Moreover,

since the GA maintains several solutions at each generation, it has the ability to generate a set of Pareto points for multi-objective optimization problems. In the context of custom NoC design, the Pareto points provide the designer with an opportunity to select a solution that corresponds to the best trade-off between low power consumption, and corresponding number of routers in the NoC.

1.2.2. System-level low power optimization (VLSI Design 04: [1], ISVLSI 04 [2], Integration, The VLSI Journal (Accepted))

In this thesis, we present two techniques for low power integrated mapping and scheduling in multiprocessor architectures. The techniques are aimed at multimedia and network processing domains that are periodic, and allow the application of loop transformations such as pipelining and unrolling. Our technique applies these loop transformations to increase the throughput of the application, and trades-off the increase for power minimization by applying system-level low power techniques namely, Dynamic Voltage Scaling (DVS), and Dynamic Power Management (DPM).

We present two techniques for system-level low power minimization. The first technique is an ILP based technique that generates optimal solutions at high runtimes. We also propose several speedup techniques to reduce the runtime of the of the formulations, with a corresponding trade-off in quality. The second technique is an iterative search based heuristic technique that generates high quality solutions at a lower runtime.

#### 1.3. Thesis organization

The remaining part of the thesis is broadly categorized into two parts. The first part, which is composed of chapters 2 through 7 defines the custom NoC design problem, and presents our

solution techniques in detail. Chapter 8 defines and presents our proposed techniques for systemlevel low power optimization. Finally, Chapter 9 summarizes the thesis, and discusses future work in this field.

#### CHAPTER 2

#### APPLICATION SPECIFIC NOC DESIGN

#### 2.1. Introduction

This chapter develops the necessary background for the NoC design problem. Automated techniques for NoC design require that a design flow is specified. The design flow in turn is governed by the application domain and interconnection architecture elements. The chapter is organized as follows. First, it presents a NoC design flow for nanoscale SoC design. This is followed by a characterization of the NoC elements to generate the power and performance models that are utilized by the automated techniques. Finally, we define the NoC design problem, and conclude the chapter.

#### 2.2. NoC design flow

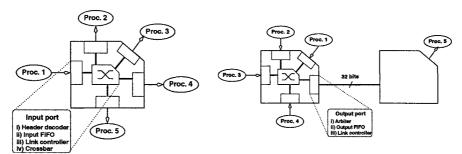

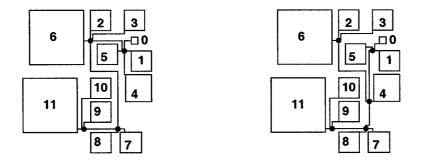

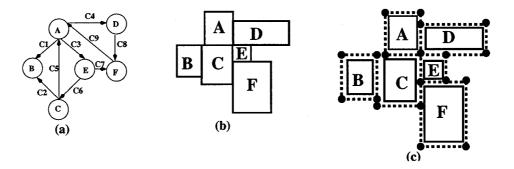

NoC architecture design is shown in Figure 2.1. The input to the communication architecture design problem is the computation architecture specification, characterized library of interconnection network components, and performance constraints. The computation architecture consists of processing and memory elements shown by rectangular blocks labeled as "P/M" in the top of the figure. Each "P/M" block is uniquely identified by a node number "n i" as denoted within each rectangle. The physical dimensions of the blocks are also specified as part of the inputs.

The directed edges between any two blocks represent the communication traces. The communication traces are annotated as "Cm(B,L)" where 'm" represents the trace number, "B" represents the bandwidth requirement, and "L" is the latency constraint. The bandwidth and latency requirements of a communication trace can be obtained by profiling the system-level specification in the context of overall application performance requirements. Applications in multimedia and network processing domains demonstrate well defined periodic communication characteristics and hence, can be easily modeled in the trace graph.

Fig. 2.1: NoC architecture design

The characterized library of interconnection architecture components is depicted on the left hand side of the figure. In nanoscale technologies, minimizing power consumption is a first order design goal along with performance maximization. Therefore, the components are characterized for both performance and power consumption. Each router architecture is characterized as follows:

- the peak bandwidth supported at input or output ports, and

- the power consumed to transfer data across the ports.

The power consumption in a port is a function of the total traffic flowing through it. Hence, the port is characterized by power consumed per unit bandwidth of traffic.

Figure 2.2 plots the power consumption of various components of the NoC for 100nm and 180nm technologies. In the figure, the X axis denotes the various components, and the Y axis denotes the corresponding dynamic energy consumption. We can infer from the plot that in nanoscale NoC architectures, the physical link will consume upwards of 30% of the total com-

Fig. 2.2: Power consumption of NoC

munication energy. The energy consumption of the physical links is dependent on its length, and the bandwidth of traffic flowing through it. The length of the link in turn is determined by the system-level floorplan. Therefore, the design of the NoC architecture must jointly address system-level floorplan and interconnection network generation. The power consumption in the physical link is a function of the bandwidth of data flowing through the link, and the length of the link. Therefore, the physical links are characterized by power consumed per unit bandwidth per unit length.

The output of the communication architecture design problem is a system-level floorplan of the final design, topology of the network, and static routing of the communication traces on the network such that the performance constraints are satisfied, and the power consumption is minimized. As shown in the bottom part of Figure 2.1, the NoC topology can either be pre-defined as shown on the right side, or it can be optimized for the application, as shown on the left.

In this thesis, we address the design of a NoC in the context of application specific SoC

architecture. Application specific SoC design offers the opportunity for incorporating custom NoC architectures that are optimized for the target problem domain, and do not necessarily conform to regular topologies. Regular topologies are suitable for general purpose architectures such as the MIT RAW [11] that include homogeneous cores. Application specific SoC architectures consist of heterogeneous cores and memory elements which have vastly different sizes. For such architectures we demonstrate that the custom NoC architecture is superior to regular architecture in terms of power and area consumption under identical performance requirements.

There are a number of limitations of the regular interconnection architecture. It assumes that all cores are of the same size, which is not the case for custom SoC. Therefore, even if the system-level topology is regular, it does not remain regular after the final floorplanning stage. The alternative option of regular layout results in large amount of area overhead. The regular topology assumes that every core has equal communication bandwidth with every other core. This does not hold in realistic applications. Regular topologies are known to support design reuse. In custom topologies, the router architecture itself is regular and can be easily parameterized (on number of ports, width of physical links, number of virtual channels and so on). In other words, custom NoC architectures also support design reuse. Therefore, this work concentrates on custom NoC topologies that are optimized for the target application.

#### 2.3. Router Architecture characterization

Figure 2.3 shows the top-level (left hand side) and detailed (right hand side) architecture of a 5-port NoC router utilized in this work. The router consists of five unit routers that communicate with the neighboring routers, and with the processor. Unit routers inside a single router are connected through a 5x5 crossbar. Data is transferred across routers or between the processor and the corresponding router by a four phase asynchronous handshaking protocol. A single unit router, and corresponding input and output ports are highlighted in the right half of the figure.

Fig. 2.3: NoC router architecture

The unit router consists of input and output link controllers, input and output virtual channels, a header decoder, and an arbiter.

Data arrives at an input virtual channel of a unit router from either the previous router or the processor connected to the same router. The header decoder decodes the header flit of the packet after receiving data from the input virtual channel, decides the packet's destination direction, and sends a request to the arbiter of the unit router in the corresponding direction for access to the crossbar. In other words, the header decoder performs the task of routing the packet. We assume that the routing strategy is an application specific scheme and the header decoder decides the output port based on the communication trace identifier (ID). The communication trace ID uniquely identifies a particular data stream flowing from a source node to the destination. Once the grant is received, the header decoder starts sending data from the input to the output virtual channel through the crossbar.

We characterize the power consumption of the unit router in 100 nm technology with the help of a cycle accurate power and performance evaluator [22]. The cycle accurate simulator was constructed by characterizing the power and performance of each of the router sub-components and physical links through Hspice simulations. In the experiment the width of the physical links

Fig. 2.5: Output port power consumption

Fig. 2.4: Input port power con-set-up sumption set-up

(consequently the width of input and output FIFO, and crossbar) is 32 bits, number of virtual channels is 2, depth of virtual channels is 4, and the number of flits in the packet is 8 (packet size 256 bits).

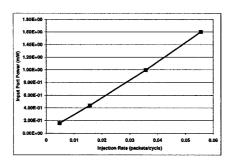

## 2.3.1. Power consumption in input port of unit router

The first experiment evaluated the power consumption of a port due to the traffic flowing into the unit router. The total power consumption due to traffic at a particular input port is the summation of the power consumed by the link controller, header decoder, input FIFO and crossbar. We considered a 5-port router with 5 processors attached to each port as shown in Figure 2.4. Processor 1 sends packets with random contents to the 4 other processors with a uniformly random distribution. Figure 2.6 plots the power consumption in the input port for the 4 components (link controller, header decoder, input FIFO, crossbar) for varying injection rate at processor 1. The delay for a particular injection rate was uniformly distributed within the mean delay interval. As can be observed from the plot the power consumption in the input port varies linearly with the injection rate.

Fig. 2.6: Input port power con-Fig. 2.7: Output port power consumption

Fig. 2.8: Link power versus injection rate

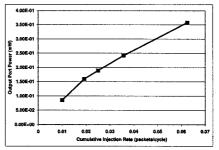

# 2.3.2. Power consumption in output port of unit router

The second experiment evaluated the power consumed at a particular output port of a unit router due to traffic flowing in the outward direction to a neighboring router or core. We considered a 5-port router with processors (1-4) attached to four input ports as shown in Figure 2.5. All the four ports inject packets that traverse through the fifth port to processor 5 attached to the neighboring router. The contents of the packets where randomly generated, and the delay for a particular injection rate was also uniformly distributed within the mean delay interval. We evaluated the total power consumption of the arbiter, output FIFO, and link controller for varying cumulative injection rate from the four processors. Figure 2.7 plots the total power consumption (for the arbiter, output FIFO, link controller) versus the cumulative injection rate. The power consumption of the output port also varies linearly with the cumulative injection rate.

Fig. 2.9: Link power versus length

Fig. 2.10: Latency for 2 routers

Fig. 2.11: Latency for 4x4 mesh

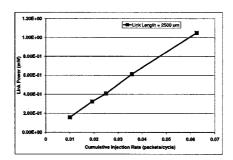

# 2.3.3. Power consumption in physical links

Figures 2.8 and 2.9 plot the variation in link power consumption versus injection rate (for a constant link length of 2.5 mm) and link length (for a constant injection rate 0.0089 packets/cycle), respectively. As can be observed from the figures the link power varies linearly with both injection rate and link length.

# 2.3.4. Latency

Figure 2.10 plots the average latency versus the injection rate for the packets in experiment 2 (Figure 2.5). Please note that the x-axis plots the injection rate due to one processor as opposed to the cumulative injection rate of the four processors as in Figure 2.7. As can be observed from the figure, the average latency remains constant until the output port gets congested. A similar

trend is observed (see Figure 2.11) when we consider a 4 x 4 mesh architecture with 16 processors that are injecting to uniformly distributed random destinations. The average network latency remains constant until the network gets congested. The network congestion is marked by a sharp increase in average latency. Our synthesis technique prevents network congestion by static routing of the communication traces subject to the peak bandwidth constraint on the router ports. Since the network is always operated in the un-congested mode, we can represent the network latency constraint in terms of router hops (such as 1 or 2) instead of an absolute number (such as 100 cycles).

### 2.4. Problem Definition

### Given:

- A directed communication trace graph G(V, E), where each  $v_i \in V$  denotes either a processing element or a memory unit (henceforth called a node), and the directed edge  $e_k = \{v_i, v_j\} \in E$  denotes a communication trace from  $v_i$  to  $v_j$ . For every  $v_i \in V$ , the height and width of the core is denoted by  $\mathcal{H}_i$  and  $\mathcal{W}_i$ , respectively.

- For every  $e_k = \{v_i, v_j\} \in E$ ,  $\omega(e_k)$  denotes the bandwidth requirement in bits per cycle, and  $\sigma(e_k)$  denotes the latency constraint in hops.

- A router architecture, where  $\eta$  denotes the number of input/output ports of the router, and  $\Omega$  denotes the peak input and output bandwidth that the router can support on any one port. Thus, each port of a router can support equal bandwidth in input and output modes. Since a node  $v \in V$  is attached to a port of a router, the bandwidth to any node from a router, and from any node to a router is less than  $\Omega$ . Two quantities  $\Psi_i$  and  $\Psi_o$  that denote the power consumed per Mbps of traffic bandwidth flowing in the input and output direction, respectively for any port of the router.

- A physical link power model denoted by  $\Psi_l$  per Mbps per mm.

- Two constants  $\mathcal{H}$  and  $\mathcal{W}$  that denote the height and width constraints on the overall dimensions of the system-level floorplan.

- A maximum allowable link length between routers to ensure a single clock cycle data transfer.

Let  $\mathcal{R}$  denote the set of routers utilized in the synthesized architecture,  $E_r$  represent the set of links between two routers, and  $E_v$  represent the set of links between routers and nodes. The objective of the NoC design problem is to:

- generate a system-level floorplan and

- a network topology  $T(\mathcal{R}, V, E_r, E_v)$ ,

such that:

- for every  $e_k = (v_i, v_j) \in E$ ,  $\exists$  a route  $p = \{(v_i, r_i), (r_i, r_j), \dots (r_k, v_j)\}$  in T,

- the bandwidth constraints on the ports of the routers are satisfied,

- the bounding box of the floorplan satisfies  $\mathcal{H}$  and  $\mathcal{W}$ , and

- the total system-level power consumption for inter-core communication is minimized.

#### 2.5. Conclusion

In this chapter, we defined a flow for NoC design in nanoscale technologies. We observed that due to the increased percentage contribution of link power consumption, and its dependence on the length of the link, system-level floorplanning must be incorporated in the flow. Based on the characterization of the router architecture, we developed power and performance models that are utilized by the automated design tools. In the following chapters, we first present a literature

survey of the existing NoC design techniques, and present our automated techniques for NoC design.

#### CHAPTER 3

#### LITERATURE SURVEY

## 3.1. Introduction

In recent years a number of researchers have proposed architectures, performance evaluation techniques and optimization approaches for NoC. This chapter classifies and presents the existing research under four categories: seminal work, router architectures, performance models, and automated optimization approaches. Our work in this thesis falls in the category of automated optimization approaches. In the following sections, we discuss previous work in the first three categories, and then compare and contrast our work with existing research in the fourth category.

#### 3.2. Seminal work

Guerrier et al. [23] presented a NoC design called SPIN that was based on fat-tree topology. They also presented the router architecture and cycle accurate performance model for their NoC design. Hemani et al. [24] presented the NoC architecture as a solution to the challenge of billion transistor ASIC design in the nanoscale era. They proposed a NoC design methodology and supported it with a case study on a hypothetical architecture. Sgroi et al. [25] discussed a platform based SoC design methodology that proposed the inclusion of NoC for supporting on-chip communication. Dally et al. [6] demonstrated the feasibility of the NoC and estimated that the NoC places an area overhead of 6.6%. Benini et al. [7] in their conceptual paper on NoC, predict that packet switched on-chip interconnection networks will be essential to address the complexity of future SoC designs. Kumar et al. [26] presented a conceptual system-level architecture that allowed a mesh-based NoC to accommodate large resources such as memory banks, FPGA areas, or high performance multi-processors. Taylor et al. [11] designed and fabricated a 4x4 mesh based NoC architecture as part of MIT RAW processor. In this thesis, we build on the research cited

above and present linear programming based techniques for automated synthesis of custom NoC architectures.

## 3.3. NoC architectures

Several researchers have proposed architectures, and related optimizations for on-chip interconnection networks. We classify the related research on NoC architectures based on the supported levels of traffic service classes, error control schemes, and power optimizations.

## 3.3.1. Architectures for best effort traffic

In this paragraph we review the NoC architectures that support only best effort traffic class. SPIN [23] [27] [28] was one of the seminal works to propose a detailed NoC architecture built with fat tree topology. Proteo [29] [30] is a VSIA-compliant NoC architecture that can be configured for ring, star, and bus topologies. xpipes [31] is a parameterized router architecture that can be utilized in arbitrary NoC topologies. The xpipesCompiler proposed by Jalabert et al. [32] is a custom topology instantiation framework. However, it does not provide any support for NoC synthesis. Therefore, our work can be considered to be complementary to xpipesCompiler.

# 3.3.2. Architectures for guaranteed throughput traffic

Nostrum [33] [34] is a protocol stack for mesh based NoC architecture that supports both best effort and guaranteed throughput traffic classes. AEthereal [35] [36] is also a mesh based NoC architecture that supports guaranteed throughput traffic by utilizing a centralized scheduler for allocation of link bandwidth.

#### 3.3.3. Architectures with error control schemes

Bertozzi et al. [37] presented power versus performance results for point-to-point error control in an on-chip bus protocol based on AMBA bus. Zimmer et al. [38] presented a fault model for NoC architecture. They also proposed a QoS scheme that treated control traffic with higher reliability than data traffic.

## 3.3.4. Architectural optimizations for low power

Worm et al. [39] proposed an adaptive low power transmission scheme for NoC that minimized the voltage swing and frequency subject to the workload requirement. Chen et al. [40] proposed a power-aware buffer policy that minimized the leakage power consumption in virtual channels. Simunic et al. [41] proposed a system-level power reduction scheme for SoC architectures with on-chip interconnection networks. Their scheme applied dynamic voltage management and dynamic voltage scaling policies based on both local and global workload information. Nilsson et al. [42] proposed a globally pseudochronous clocking scheme to reduce latency and power consumption in mesh based architectures.

Existing research on NoC architectures and their optimization concentrate on architectures that conform to a regular topology. Communication trace driven application specific NoCs need not conform to a regular topology. In this thesis, we present techniques to generate irregular topologies that minimize the communication power and area of the NoC.

## 3.4. Performance Evaluation

[43] [44] [45] [46] presented performance evaluation models for micro-interconnection networks that do not consider NoC architectures. Wassal et al. [47] proposed system-level performance and power models for a shared-memory internet protocol/asynchronous transfer mode switching fabric. Ye et al. [48] analyzed the power consumption in the switch fabrics of network

routers and proposed system-level models for the same. Pamunuwa et al. [49] performed a system level analysis and estimated the wiring overhead and the gate count for implementing mesh-based NoC architecture. Wang et al. [50] proposed a power-performance simulator for interconnection network called Orion. Bolotin et al. [51] proposed analytical models for system-level performance and cost estimation of NoC architectures.

## 3.5. Automated design techniques

Existing automated design techniques for regular topologies have primarily focused on mesh based NoC architectures. Hu et al. [52] proposed a branch and bound technique for core to router mapping on mesh based NoC architectures. Murali et al. [53] presented a heuristic technique called NMAP for core to router mapping, and routing in mesh based architectures. Ascia et al. [54] presented a genetic algorithm based technique for the same problem. Guz et al. [55] presented a technique for link capacity allocation for mesh based NoC architectures. Murali et al. [56] explored the problem of mapping cores on to mesh based NoCs where each core supports multiple applications. They sum the bandwidth requirements of different applications to generate a single application, and based on the single application, invoke an existing heuristic that maps cores onto the mesh. Angiolini et al. [57] compared the power and performance of mesh based NoC architectures with AMBA bus architectures. Steenhof et al. [58] predicted NoC as a solution to high-end consumer electronics systems, and presented a SoC with mesh based NoC for a TV system architecture. In contrast to the above cited research, our techniques generate application specific custom NoC architectures that are optimized for a given application domain.

In recent years, researchers have turned their focus on application specific NoC design. Benini et al. [59] presented a survey of design techniques for application specific NoC architectures. Pinto et al. [60] proposed a technique for synthesis of point to point links that utilize at most two routers between source and sink. Thus, their problem formulation does not address routing.